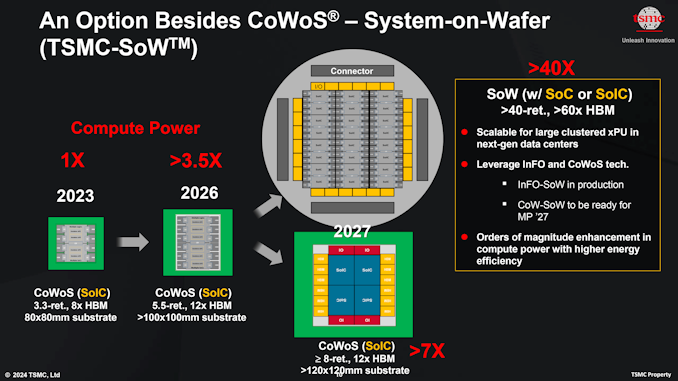

TSMC oferă tehnologia sa de integrare System-on-Wafer, InFO-SoW, din 2020. Deocamdată, doar Cerebras și Tesla au dezvoltat modele de procesoare la scară de wafer folosind-o. Deși au performanțe și eficiență energetică fantastice, procesoarele la scară de wafer sunt extrem de complexe de dezvoltat și produs. Dar TSMC consideră că nu numai că modelele la scară de wafer vor crește în utilizare, dar că megatendințele precum AI și HPC vor necesita soluții și mai complexe: modele de sisteme pe wafer stivuite vertical.

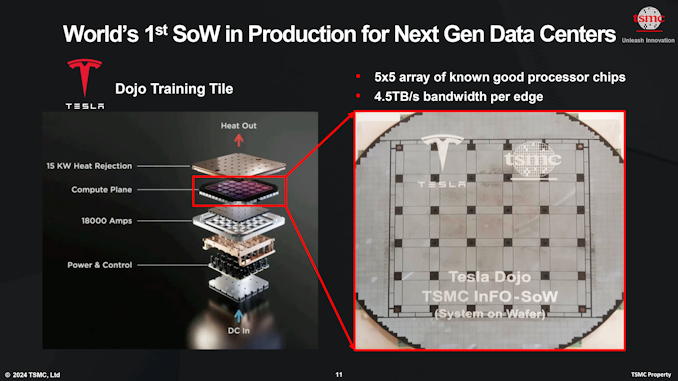

Procesoarele Tesla Dojo la scară de wafer – primele soluții bazate pe tehnologia InFO-SoW de la TSMC care sunt în producție de masă – au o serie de avantaje față de sistemele în pachete (SiP) tipice, inclusiv comunicații core-to-core cu latență redusă și lățime de bandă mare, performanțe foarte ridicate și densitate de lățime de bandă foarte mare, impendență relativ scăzută a rețelei de alimentare, eficiență ridicată a performanțelor și redunabilitate.

Dar cu InFO-SoW și alte metode de integrare la scară de placă, proiectanții de procesoare trebuie să se bazeze exclusiv pe memoria pe cip. Acest lucru este perfect adecvat pentru multe aplicații, dar s-ar putea să nu fie suficient pentru sarcinile de lucru de inteligență artificială de ultimă generație. În plus, în cazul InFO-SoW, întreaga placă trebuie procesată cu ajutorul unei singure tehnologii de fabricare, ceea ce poate să nu fie optim sau să fie prea costisitor pentru anumite proiecte.

Astfel, cu platforma sa de sistem pe placă de următoarea generație, TSMC intenționează să reunească două dintre tehnologiile sale de ambalare: InFO-SoW și System on Integrated Chips (SoIC), ceea ce îi va permite să suprapună memoria sau logica peste un sistem pe placă (system-on-wafer) folosind metoda sa Chip-on-Wafer (CoW). Tehnologia CoW-SoW, pe care compania a anunțat-o în cadrul Simpozionului său nord-american de tehnologie, va fi gata pentru producția de masă în 2027.

Deocamdată, TSMC vorbește mai ales despre procesoare la scară de wafer de nuntă cu memorie HBM4. Și având în vedere că stivele HBM4 vor avea o interfață pe 2048 de biți, integrarea mai strânsă a acesteia cu logica este un aspect pe care industria îl ia în considerare.

“Așadar, în viitor, utilizarea integrărilor la nivel de placă [va permite] clienților noștri să integreze și mai multă logică și memorie împreună”, a declarat Kevin Zhang, vicepreședinte pentru dezvoltarea afacerilor la TSMC. “SoW nu mai este o ficțiune, acesta este un lucru la care lucrăm deja cu clienții noștri [pentru] a produce unele dintre produsele deja existente. Acest lucru credem că, prin valorificarea tehnologiei noastre avansate de integrare la nivel de plachetă, putem oferi clienților noștri o cale foarte importantă care le permite să continue să își crească capacitatea de a aduce mai mult calcul, un calcul mai eficient din punct de vedere energetic, în clusterul lor de inteligență artificială sau [supercomputer].”

Lecturi conexe

- Tehnologia de 1,6nm a TSMC anunțată pentru sfârșitul anului 2026: A16 cu “Super Power Rail” Backside Power

- Actualizare TSMC 2nm: N2 în 2025, N2P pierde puterea din spate și NanoFlex aduce celule optime

- TSMC pregătește un proces N4C de 4nm mai ieftin pentru 2025, vizând o reducere a costurilor cu 8,5%.