Tehnologiile avansate de ambalare 3D-stacked system-on-integrated chips (SoIC) ale TSMC vor evolua rapid. Într-o prezentare făcută în cadrul recentului simpozion tehnologic al companiei, TSMC a prezentat o foaie de parcurs care va duce tehnologia de la un pas actual de 9μm până la un pas de 3μm până în 2027, stivuind împreună combinații de matrițe A16 și N2.

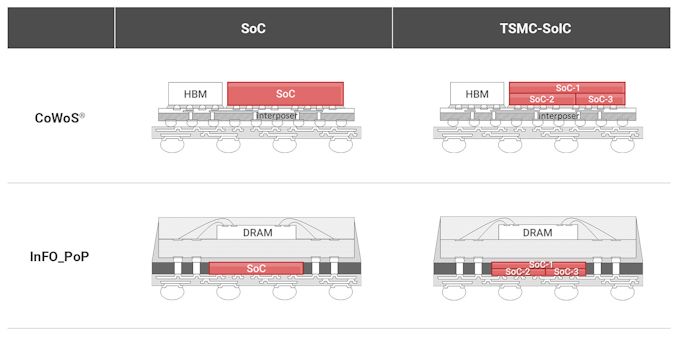

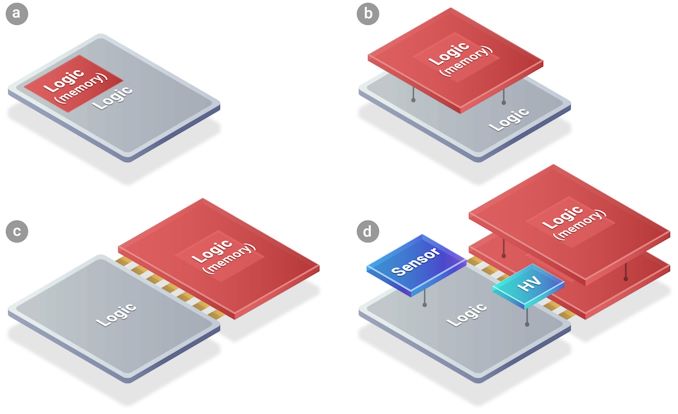

TSMC dispune de o serie de tehnologii avansate de ambalare, inclusiv 2.5D CoWoS și 2.5D/3D InFO. Poate că cea mai interesantă (și complexă) metodă este tehnologia SoIC (system-on-integrated chips) cu stivuire 3D, care reprezintă implementarea de către TSMC a lipirii hibride a plachetelor. Lipirea hibridă permite ca două dispozitive logice avansate să fie stivuite direct unul peste celălalt, permițând conexiuni ultra-dense (și ultra-scurte) între cele două cipuri, și este destinată în principal pieselor de înaltă performanță. Deocamdată, SoIC-X (bumpless) este utilizat pentru anumite aplicații, cum ar fi tehnologia 3D V-cache a AMD pentru procesoare, precum și pentru produsele de inteligență artificială din seria Instinct MI300. Și, în timp ce adoptarea este în creștere, generația actuală a tehnologiei este constrânsă de limitările privind dimensiunile matrițelor și pitch-urile de interconectare.

Dar se așteaptă ca aceste limitări să cedeze rapid, dacă totul decurge conform planului pentru TSMC. Tehnologia SoIC-X va avansa rapid și, până în 2027, va fi posibilă asamblarea unui cip care să împerecheze o matriță superioară de dimensiunea unei retușuri, realizată cu tehnologia de vârf A16 (clasa 1,6 nm) de la TSMC, pe o matriță inferioară produsă cu N2 (clasa 2 nm) de la TSMC. Aceste matrițe, la rândul lor, vor fi conectate folosind TSV-uri (TSV-uri) cu pas de 3μm, de trei ori mai mare decât densitatea dimensiunii pasului de 9μm din prezent. Astfel de interconexiuni mici vor permite un număr mult mai mare de conexiuni în ansamblu, crescând considerabil densitatea lățimii de bandă (și, prin urmare, performanța) a cipului asamblat.

| Foaia de parcurs SoIC-X a TSMC Date furnizate de TSMC (compilate de AnandTech) | ||||||||

| 2022 | 2023 | 2024 | 2025 | 2026 | 2027 | |||

| Top Die | N7 | N5 | N4 | N4 | N2 | A16 | ||

| Partea inferioară Die | N7 | ≥N6 | ≥N5 | ≥N4 | ≥N3 | ≥N2 | ||

| Bond Pitch | 9 μm | 9 μm | 6 μm | 6 μm | 4,5 μm | 3 μm | ||

| Dimensiune* | 0,1 reticul 0,1 | 0,4 reticul 0,4 | 0.8 reticul 0.8 | 1 reticul | 1 reticul | 1 reticul | ||

*TSMC consideră că dimensiunea reticulului este de aproximativ 830 mm2.

Tehnicile îmbunătățite de lipire hibridă sunt menite să le permită marilor clienți HPC ai TSMC – AMD, Broadcom, Intel, NVIDIA și altele asemenea – să construiască proiecte de procesoare dezagregate mari și ultra-dense pentru aplicații solicitante, în care distanța dintre matrițe este critică, la fel ca și spațiul total utilizat. Între timp, pentru aplicațiile în care contează doar performanța, seva fi posibilă plasarea mai multor pachete SoIC-X pe un interpozitor CoWoS.pentru a obține performanțe îmbunătățite la un consum mai mic de energie.

Pe lângă dezvoltarea tehnologiei sale de ambalare SoIC-X, destinată dispozitivelor care necesită performanțe extreme, TSMC va lansa în viitorul apropiat și procesul de ambalare SoIC-P. SoIC-P este conceput pentru aplicații mai ieftine și cu performanțe mai scăzute care doresc totuși o suprapunere 3D, dar nu au nevoie de performanțele și complexitatea suplimentare care vin odată cu conexiunile TSV cupru-cupru fără goluri. Această tehnică de împachetare va permite unei game mai largi de companii să utilizeze SoIC și, deși TSMC nu poate vorbi despre planurile clienților săi, o versiune mai ieftină a tehnologiei ar putea să o facă accesibilă pentru aplicații de consum mai atente la costuri.

Conform planurilor actuale ale TSMC, până în 2025, compania va oferi o tehnologie SoIC-P bumped față-spate (F2B) capabilă să asocieze o matriță superioară N3 (clasa 3nm) cu dimensiunea de 0,2 particule cu o matriță inferioară N4 (clasa 4nm), care vor fi conectate cu ajutorul unor micro-bumps (µbumps) cu pas de 25μm. În 2027, TSMC va introduce tehnologia SoIC-P bumped face-to-face (F2F), care va fi capabilă să plaseze o matrice superioară N2 pe o matrice inferioară N3 cu un pas de 16μm.

| Foaia de parcurs SoIC-P a TSMC Date furnizate de TSMC (compilate de AnandTech) | ||||

| 2025 | 2027 | |||

| Top Die | N3 | N2 | ||

| Partea inferioară Die | ≥N4 | ≥N3 | ||

| Bond Pitch | 25 μm | 16 μm | ||

| Dimensiune* | 0,2 reticul 0,2 | 0,4 reticul 0,4 | ||

| Orientarea | față în față | față în față | ||

| Calificare Timp | Q4 2024 for mobile SoC | Q2 2026 pentru HPC | ||

*TSMC consideră că dimensiunea reticulului este de aproximativ 830 mm2

Mai sunt multe de făcut pentru ca SoIC să devină mai popular și mai accesibil în rândul dezvoltatorilor de cipuri, inclusiv pentru a continua să se îmbunătățească interfețele de tip die-to-die. Dar TSMC pare să fie foarte optimistă în ceea ce privește adoptarea SoIC de către industrie și se așteaptă ca aproximativ 30 de modele SoIC să fie lansate până în 2026 – 2027.